4 bit ripple counter verilog for loop

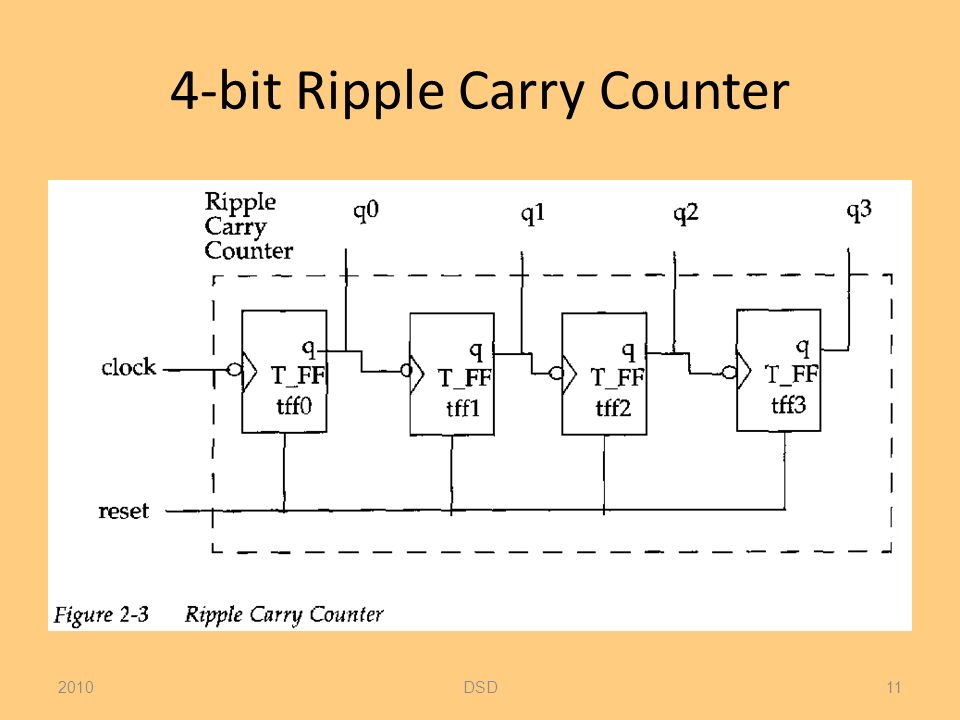

These are known as tally counters. A decade counter is one that counts in decimal digits, rather than binary. Figure 4-bit Ripple Carry Counter Figure shows that the T-flipflop is built with one D-flipflop and an inverter gate. This counter will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and a transition from 1 to 0. Retrieved from " https:

Many types of counter circuits are available as digital building blocks, for example a number of chips in the series implement different counters. The result is called a ripple counter, which can count to 2 n - 1 where n is the number of bits flip-flop stages in the counter. Figure 4-bit Ripple Carry Counter Figure shows 4 bit ripple counter verilog for loop the T-flipflop is built with one D-flipflop and an inverter gate. An n-bit ripple carry adder will have 2n gate levels. The code contains instantiation of four T-FF modules.

One of the most popular methods to reduce delay is to use a carry lookahead mechanism. Then we built a 4-bit full ripple carry adder. Each is useful for different applications. This circuit can store one bit, and hence can count from zero to one before it overflows starts over from 0. We design a 4-bit ripple counter by using negative edge- triggered flip-flops.

The Art of Electronics. Views Read Edit View history. The code is shown in Figure Ripple counters suffer from unstable outputs as the overflows "ripple" from stage to stage, but they do find frequent application as dividers for clock signals, where the instantaneous count is unimportant, but the division ratio overall is to clarify this, a 1-bit counter is exactly equivalent to a divide by two circuit; the output frequency is 4 bit ripple counter verilog for loop half that of the input when fed with a regular train of clock pulses.

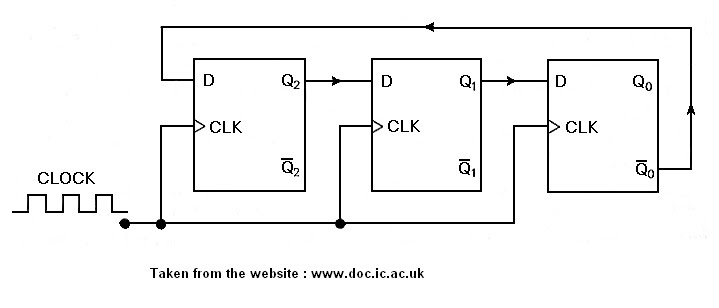

We design it using Verilog dataflow statements and test it with a stimulus module. Synchronous counters can also be implemented with hardware finite-state machineswhich are more 4 bit ripple counter verilog for loop but allow for smoother, more stable transitions. This page was last edited on 3 Mayat We design a 4-bit ripple counter by using negative edge- triggered flip-flops. You can continue to add additional flip-flops, always inverting the output to its own input, and using the output from the previous flip-flop as the clock signal.

Such counters were used as odometers for bicycles and cars and in tape recordersfuel dispensersin production machinery as well as in other machinery. By encapsulating functionality inside a module, we can replace the gate-level module with a dataflow module without affecting the other modules in the simulation. For the first and last, it doesn't matter whether the FSM is a deterministic finite automaton or a nondeterministic finite automaton.

This counter will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and 4 bit ripple counter verilog for loop transition from 1 to 0. Putting them together yields a two-bit counter:. We again illustrate two methods to describe a 4-bit full adder by means of dataflow statements. A decade counter may have each that is, it may count in binary-coded decimalas the integrated circuit did or other binary encodings. Logic equations for implementing the carry lookahead mechanism can be found in any logic design book.